## **PhanTAM-9XXC Series**

15.6", 21.5" Fanless Stainless Steel Display

## **User Manual**

Release Date Revision

June. 2023 V1.1

# **Revision History**

| Reversion | Date       | Description                    |  |

|-----------|------------|--------------------------------|--|

| 1.0       | 2023/05/05 | Official Version               |  |

| 1.1       | 2023/06/15 | 1.2 delete 2.5" SSD for option |  |

## Warning!

This equipment generates, uses and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, it may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Electric Shock Hazard – Do not operate the machine with its back cover removed. There are dangerous high voltages inside.

#### **Dear Valued Partners**

Thank you for supporting APLEX Technology. Kindly note for PhanTAM series, the pressure testing screw is loosen for half turn before shipment. The purpose is to avoid potential quality concerns caused by radical air pressure change during transportation. This especially applies to air shipment with unpressurized cabin.

Upon receiving the system, please tighten the pressure testing screw before deployment to ensure 100% functionality.

#### Here is our suggestion:

- 1. Prepare a 3mm hex screwdriver

- 2. Tighten the screw (indicated in circle) clockwise until it is well in place

- 3. Recommend torque is 8~10 kgf-cm

Apologies for any inconveniences caused and thank you for your cooperation.

#### **Yours Sincerely**

## **Table of Contents**

| Revision History                         |                     |

|------------------------------------------|---------------------|

| Warning! Logistic Statement              |                     |

| Chapter 1                                | Getting Started     |

| 1.1 Features                             | 6                   |

| 1.2 Specifications                       |                     |

| 1.3 Dimensions                           | 10                  |

| 1.4 Brief Description of PhanTAM-9XXC Se | ries11              |

| Chapter 2                                | <u> Hardware</u>    |

| 2.1 Motherboard Introduction             | 13                  |

| 2.2 Specifications and Dimensions        |                     |

| 2.3 Jumpers and Connectors Locations     |                     |

| 2.4 Jumpers setting and Connectors       | 19                  |

| Chapter 3                                | BIOS Setup          |

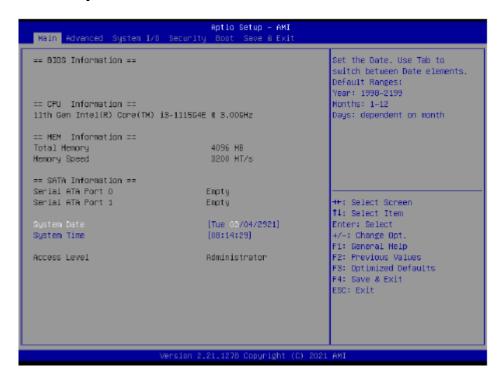

| 3.1 System Test and Installation         |                     |

| 3.2 AMI BIOS Setup                       |                     |

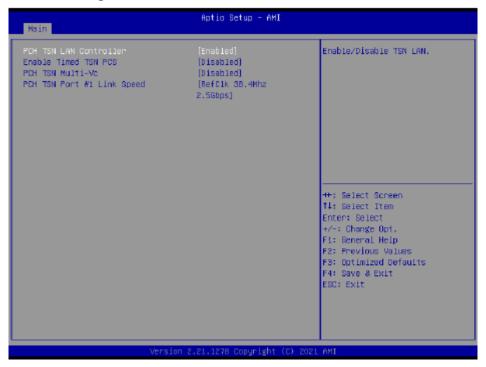

| 3.3 Setup Submenu: Main                  |                     |

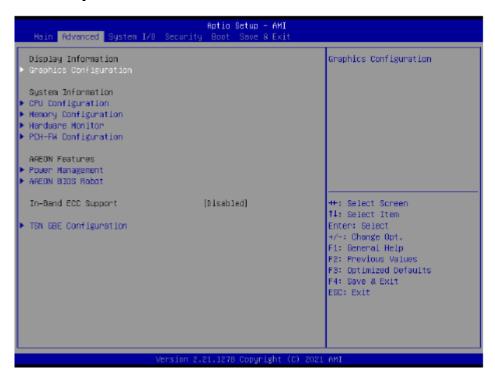

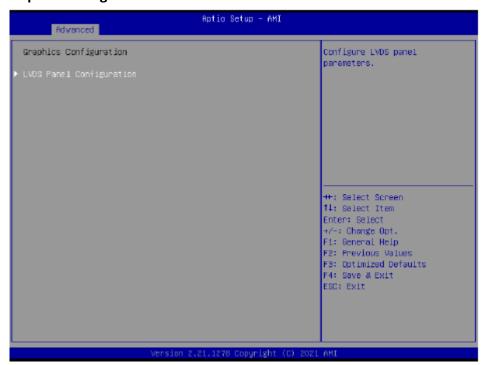

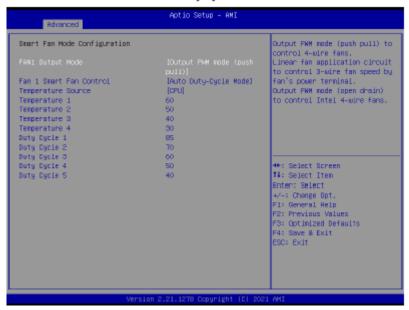

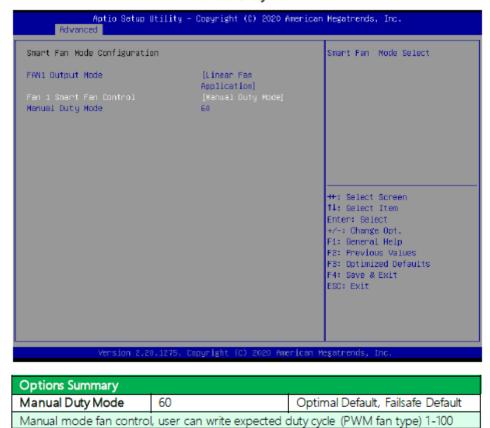

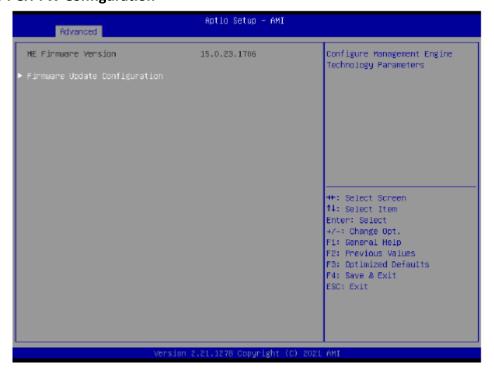

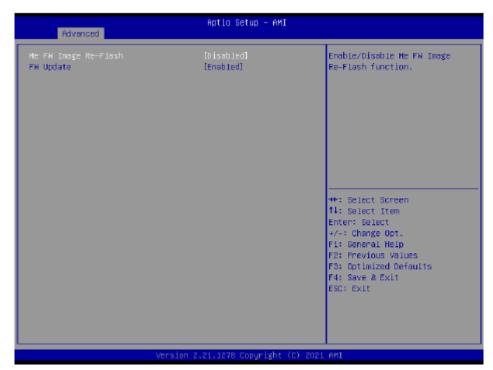

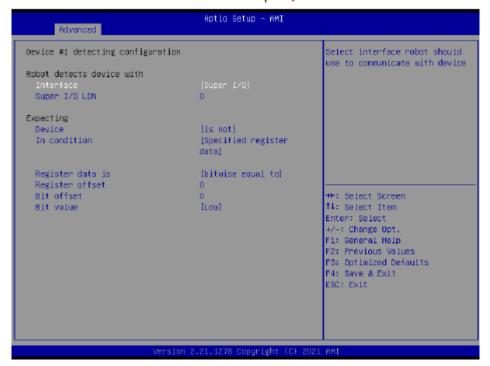

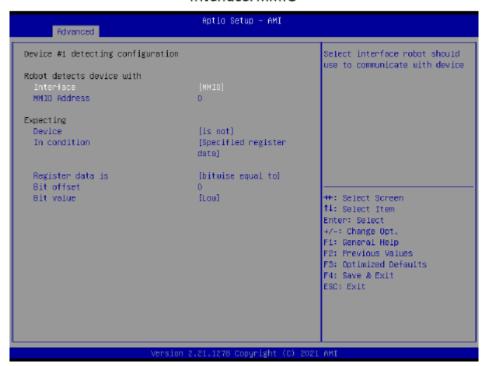

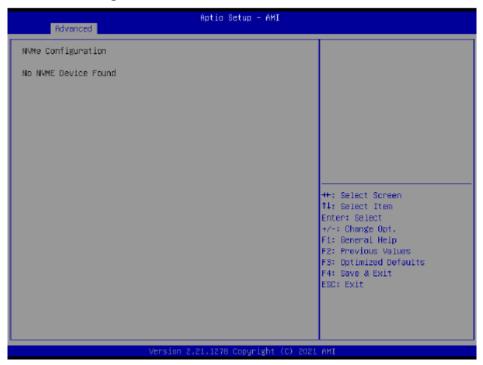

| 3.4 Setup Submenu: Advanced              | 43                  |

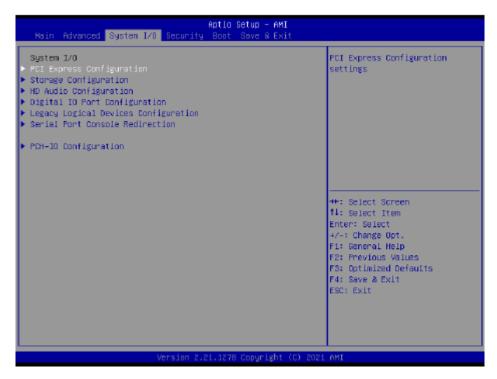

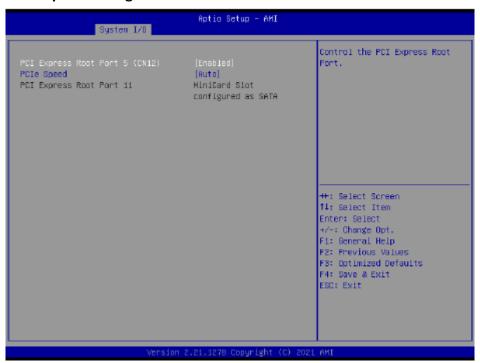

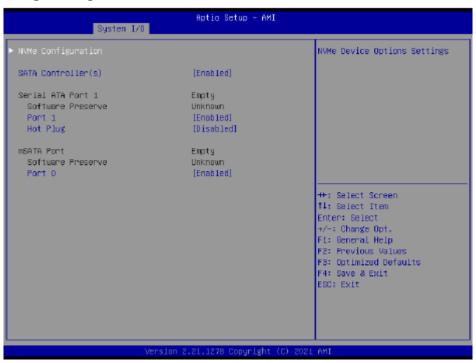

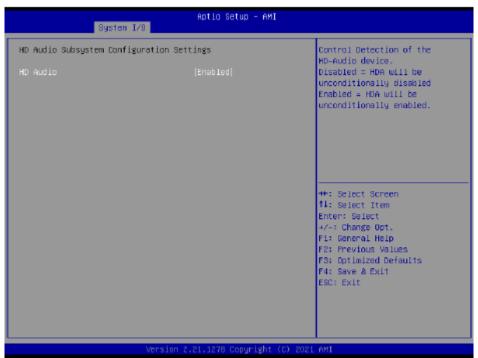

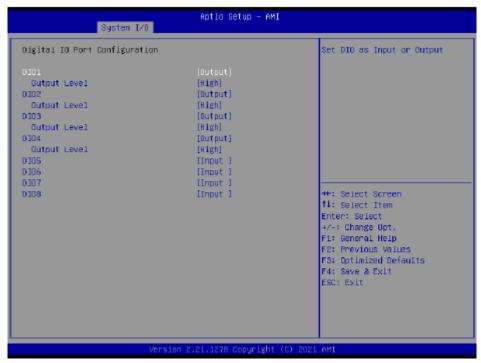

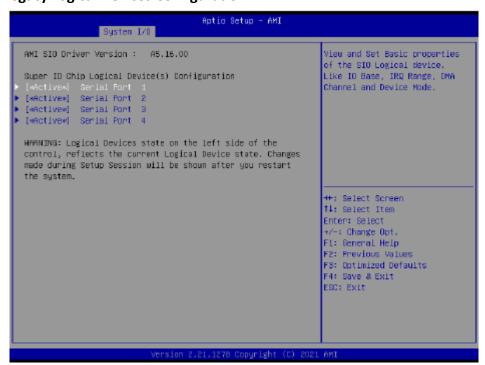

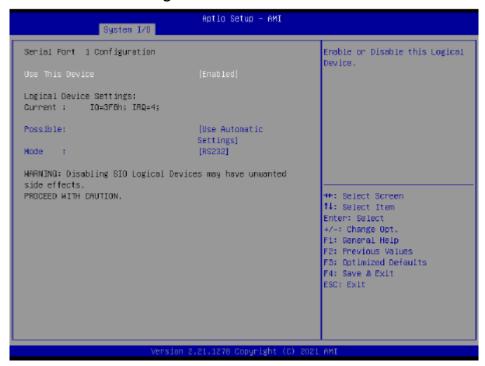

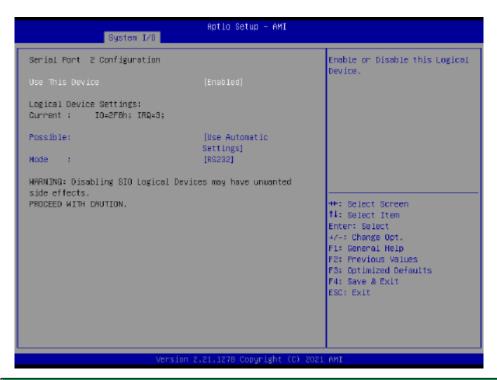

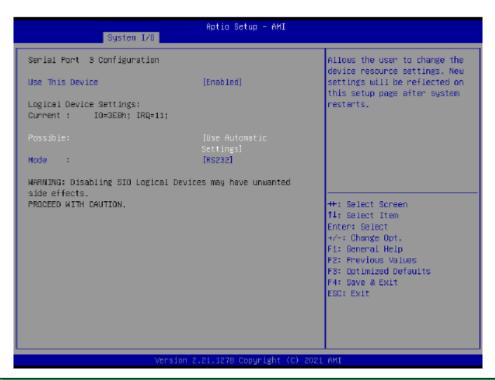

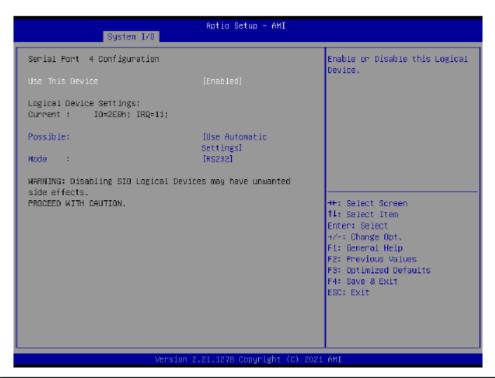

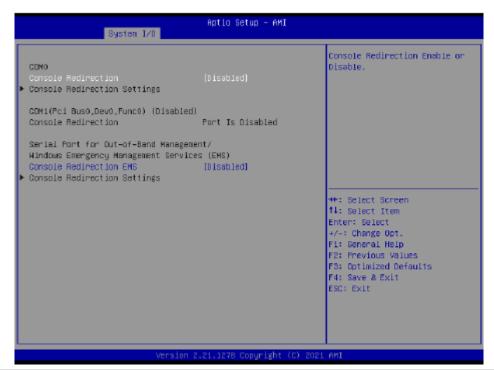

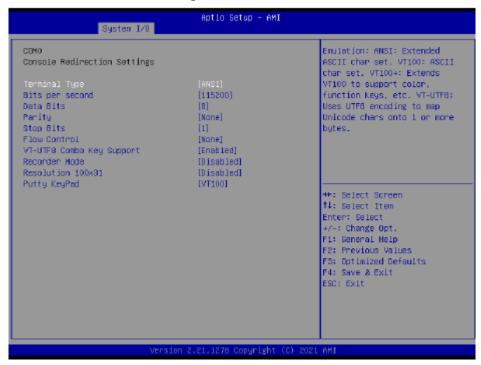

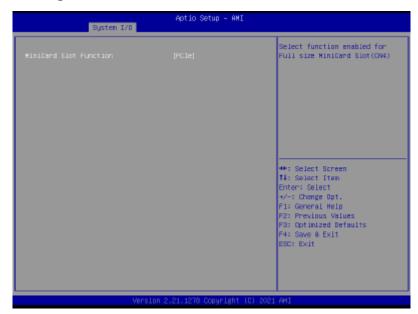

| 3.5 Setup Submenu: System I/O            | 66                  |

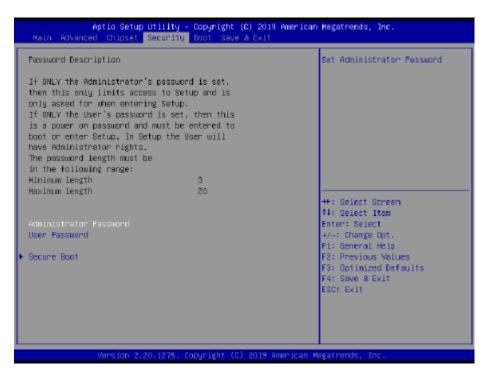

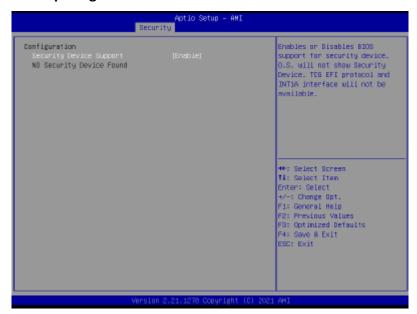

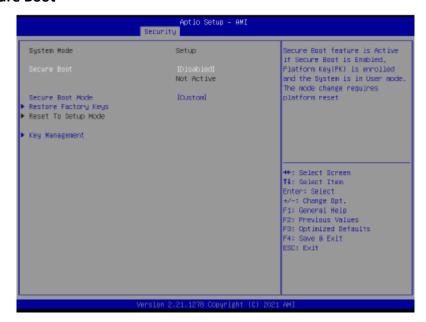

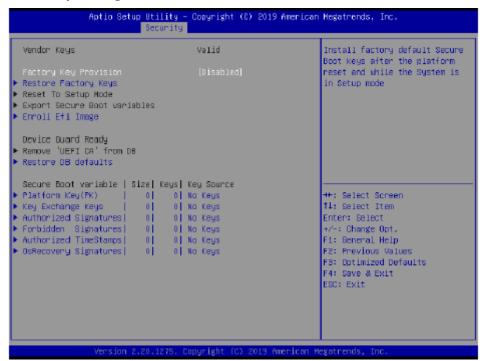

| 3.6 Setup Submenu: Security              | 78                  |

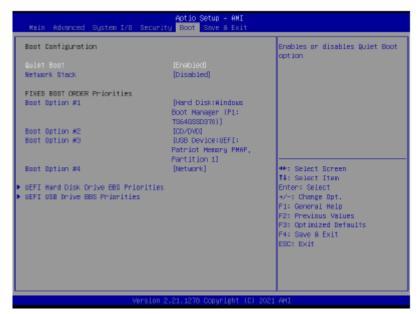

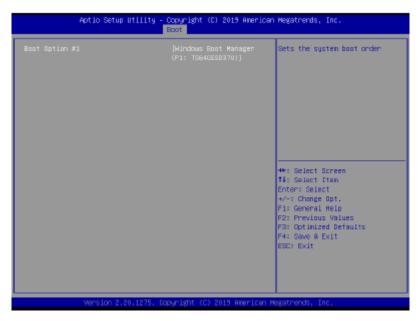

| 3.7 Setup Submenu:Boot                   |                     |

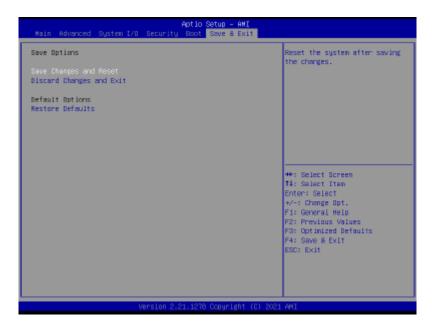

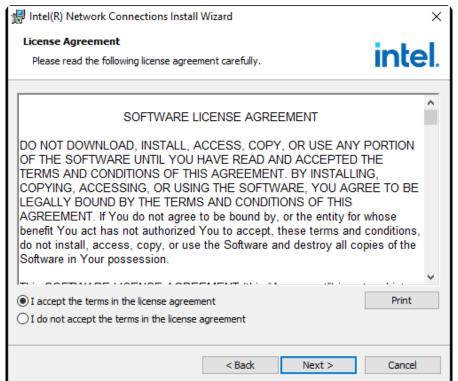

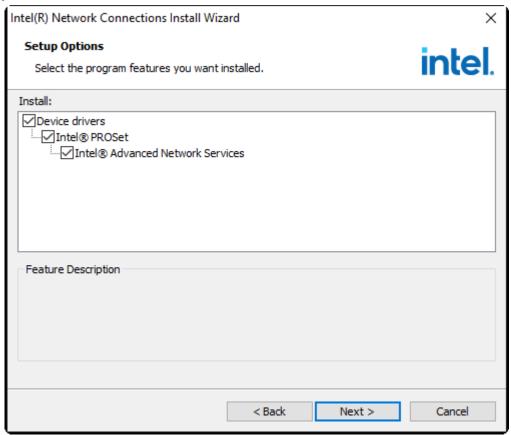

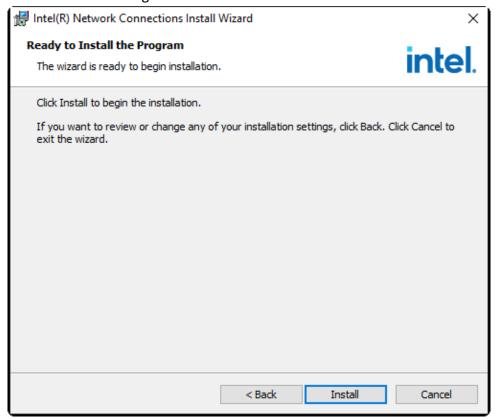

| 3.8 Setup Submenu: Save&Exit             | 84                  |

| Chapter 3 Inst                           | allation of Drivers |

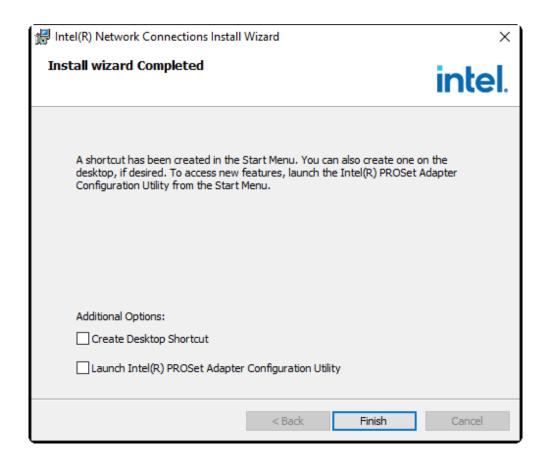

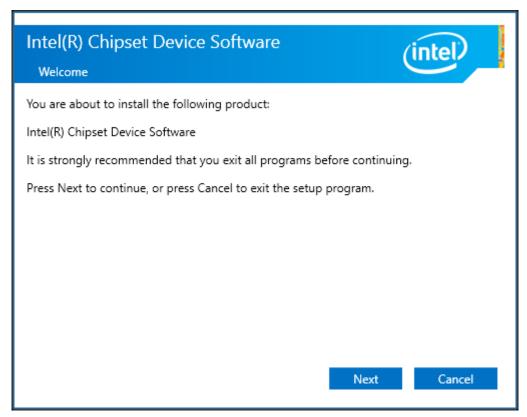

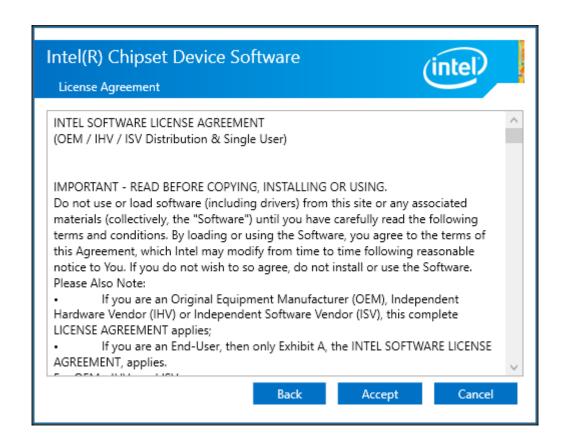

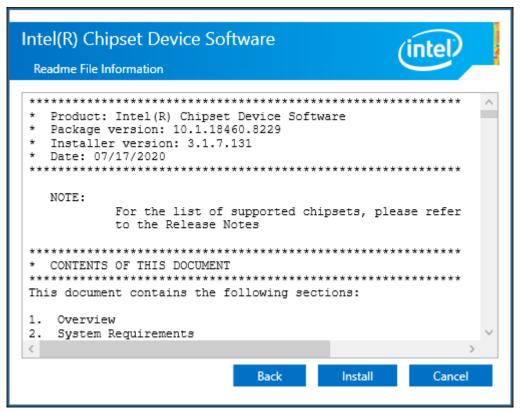

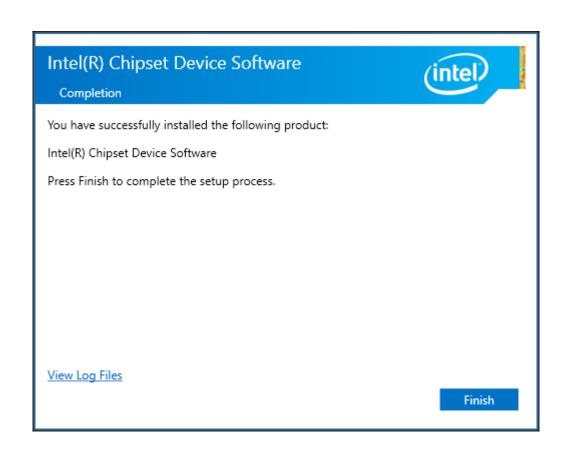

| 4.1 Intel®Chipset Device Software        | 85                  |

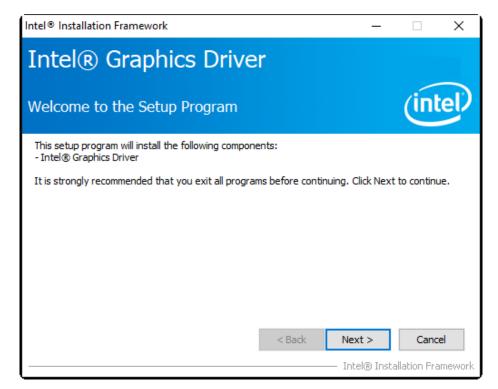

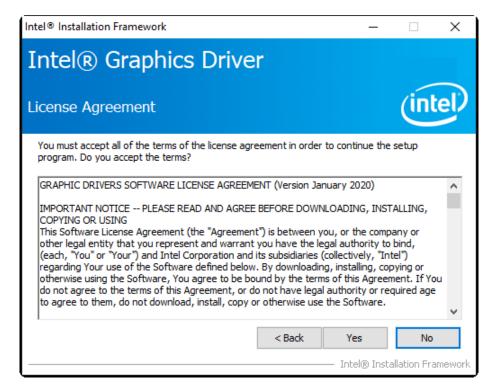

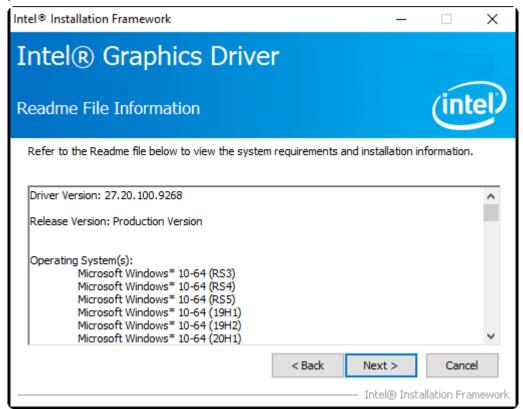

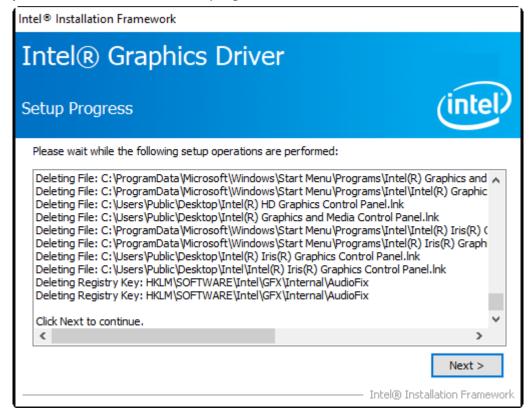

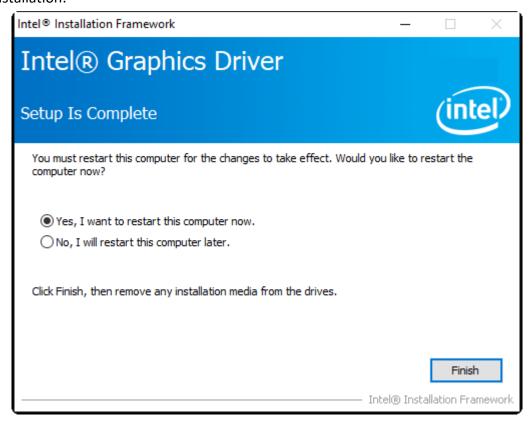

| 4.2 Intel®VGA Chipset                    | 88                  |

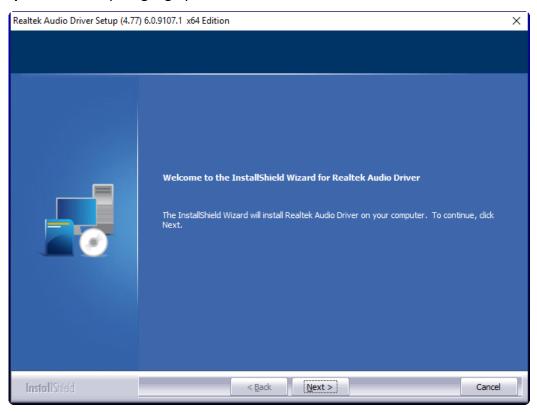

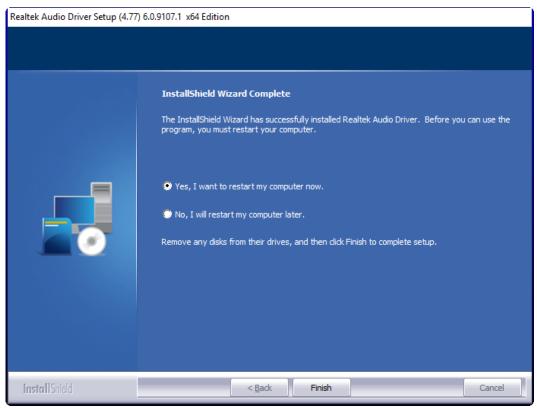

| 4.3 Realtek Audio Driver                 | 91                  |

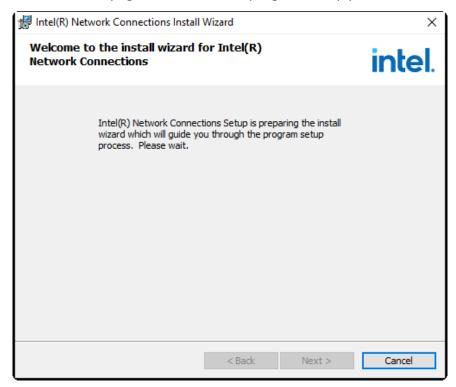

| 4.4 Intel®LAN Driver                     | 92                  |

| Figures                                  |                     |

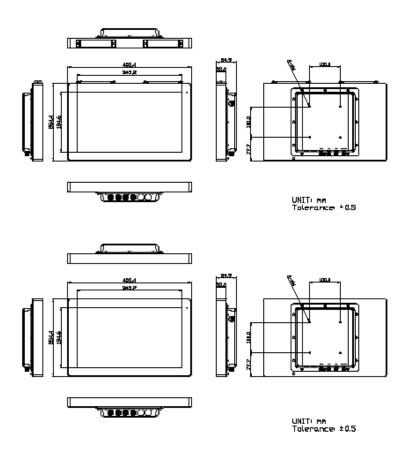

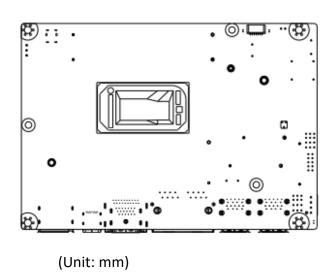

| Figure 1.1: Dimensions of PhanTAM-9160   | CP/R(H)10           |

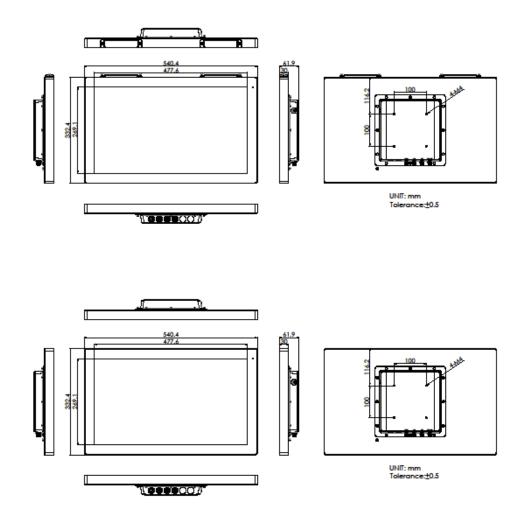

| Figure | 1.2: Dimensions of PhanTAM-921CP/R(H)              | 11 |

|--------|----------------------------------------------------|----|

| Figure | 1.3: Front View of PhanTAM-9XXC Series             | 12 |

| Figure | 1.4: Rear View of PhanTAM-916C Series              | 12 |

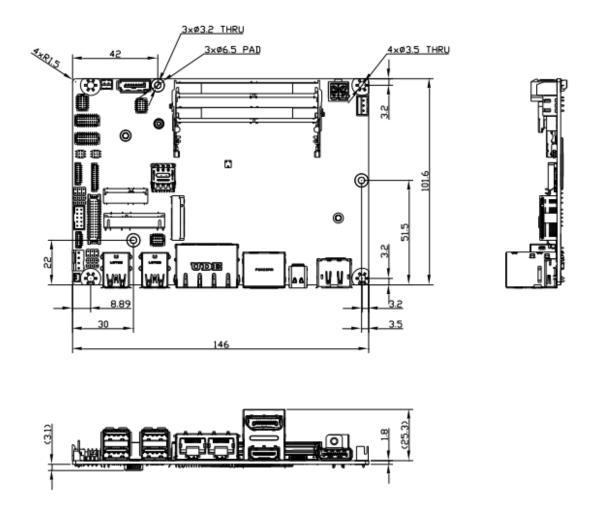

| Figure | 2.1: Motherboard Dimensions                        | 16 |

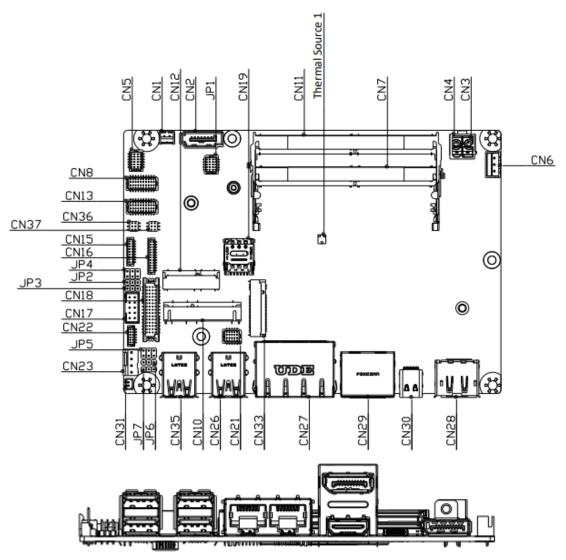

| Figure | 2.2: Jumpers and Connectors Locations-Board Top    | 17 |

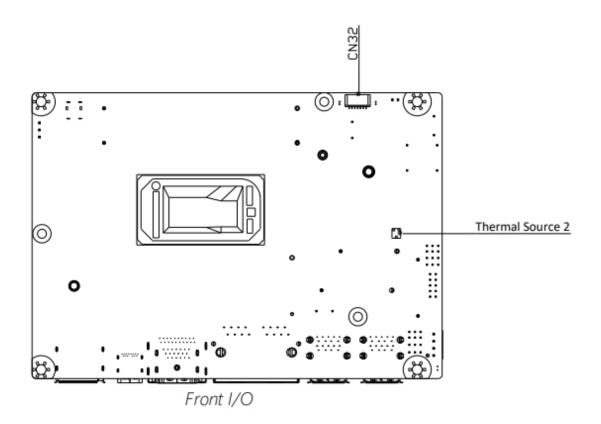

| Figure | 2.3: Jumpers and Connectors Locations-Board Bottom | 18 |

## Chapter 1\_\_\_\_

## **Getting Started**

#### 1.1 Features

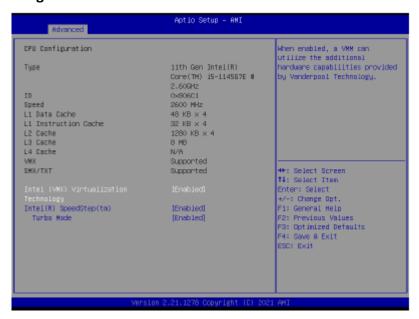

- 15.6"/21.5" Intel® 11<sup>th</sup> Gen. Fanless Stainless Steel display

- Gap-free sealing and Slim Front Frame architecture at front bezel

- IP66/IP69K Full sealed with Anti-Corrosion Enclosure

- Special Hygienic Screws on I/O Cover

- Optional Robust Waterproof Wireless Antenna Cover and Air Pressure Balance

Screw

- M12 Connectors with waterproof cover and chain

- DC 9~36V wide range power input

## 1.2 Specifications

|                      | PhanTA                 | M-916CP/R(H)                                                     | PhanTAM-921CP/R(H)                    |  |

|----------------------|------------------------|------------------------------------------------------------------|---------------------------------------|--|

| System               |                        |                                                                  |                                       |  |

| CPU                  |                        | Onboard Intel® 11 <sup>th</sup> Gen (Tiger Lake-UP3) Processors: |                                       |  |

|                      | C                      | Core™ i5-1145G7E (4C, 1.                                         | .5 GHz, up to 4.1GHz, 28W TDP)        |  |

|                      | C                      | Core™ i3-1115G4E (2C, 2.                                         | .2 GHz, up to 3.9GHz, 28W TDP)        |  |

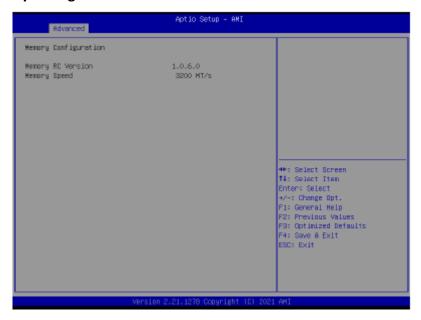

| Memory               | 2 x SC                 | )-DIMM up to 64GB DDR                                            | 4 3200MHz(Dual Channel, Non-ECC)      |  |

| Graphics             |                        | Intel®Iri                                                        | s®Xe Graphics                         |  |

|                      |                        | Intel UHD Graphic                                                | s for 11 <sup>th</sup> Gen Processors |  |

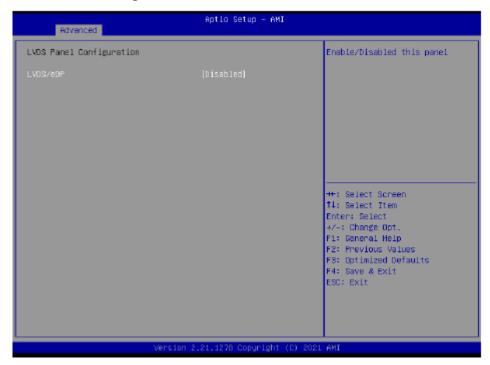

| LVDS                 |                        | 1 x 18/24                                                        | bit Dual Channel                      |  |

| Outside IO Port – St | tandard M12 I/O Conn   | nector on the Rear Side                                          |                                       |  |

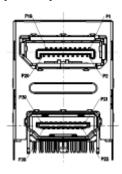

| USB                  | 1 x M12 8-pin for 2x U | SB2.0 with waterproof cover and                                  |                                       |  |

|                      |                        | chain                                                            |                                       |  |

|                      |                        | USB1/2:                                                          |                                       |  |

|                      | CN1                    | Pin Define                                                       | 8-2-1                                 |  |

|                      | 1                      | USB1 5V                                                          | 3                                     |  |

|                      | 3                      | D1-                                                              |                                       |  |

|                      | 4                      | D1+                                                              | 4-56                                  |  |

|                      | 7                      | GND                                                              | Pin Assignments<br>Front View 正視圖     |  |

|                      | 2                      | USB2 5V                                                          |                                       |  |

|                      | 5                      | D2-                                                              |                                       |  |

D2+

|                       | 8 GN                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial/Parallel       | 1 x M12 8-pin COM1, RS-232/42      | /485, Default RS-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | 232, with waterproof cove          | and chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | Pin Defin                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 1 DCD                              | 8-2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | 2 RXD                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | 3 TXD                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 4 DTR                              | 4-5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | 5 GND                              | Pin Assignments<br>Front View 正視圖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | 6 DSR                              | The state of the state of the state of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                       | 7 RTS                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 8 CTS                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

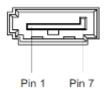

| LAN                   | 1 x M12 8-pin for LAN with waterpr | of cover and chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | LAN:                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | Pin Defin                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 1 LAN1_0                           | 8 2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | 2 LAN1_0                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | 3 LAN1_1                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 4 LAN1_1                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 5 LAN1_2                           | Pin Assignments<br>Front View 正視圖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | 6 LAN1_2                           | to the same of the |

|                       | 7 LAN1_3                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 8 LAN1_3                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

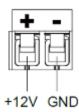

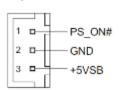

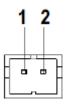

| Power                 | 1 x M12 3-pin for DC power with    | waterproof cover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | and chain                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | Pin Define                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 1 NC                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 3 VCC                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 4 GND                              | Pin Assignments Front View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

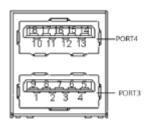

| Option I/O Port (Eith |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | 2 x optional blank M12 conn        | ectors with waterproof cap for selecting two from the following                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

options:

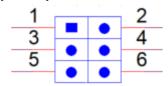

| Onting                 |                                                 | 2 v l                   | ISB 2.0                                       |

|------------------------|-------------------------------------------------|-------------------------|-----------------------------------------------|

| Option                 | 2 x USB 2.0<br>1 x USB 3.2 Gen1                 |                         |                                               |

|                        | 1 x LAN (POE for option)                        |                         |                                               |

|                        | 1 x COM                                         |                         |                                               |

|                        | 1 x HDMI                                        |                         |                                               |

| Storage Space          |                                                 |                         |                                               |

| Storage                |                                                 | 1 x M.2 M-Key 2280      | ) (PClex4 as default)                         |

| Expansion              |                                                 |                         |                                               |

| Expansion Slot         | 1 x M.2 2230 E-Key (                            | PClex2+USB2.0) socket f | for WIFI/BT and Antenna at rear side (option) |

|                        | 1 x Full-size mi                                | PCIe/mSATA with NANO    | -SIM (mPCle as default, select by BIOS)       |

| RFID module            |                                                 | RFID module design or   | the front side (option)                       |

| Display – Standard LC  | D                                               |                         |                                               |

| Display Type           | 15.6" 1                                         | FT LCD                  | 21.5" TFT LCD                                 |

| Max. Resolution        | 1366 x 768                                      | 1920 x 1080             | 1920 x 1080                                   |

| Max. Color             | 16.7M                                           | 16.2M                   | 16.7M                                         |

| Luminance (cd/m²)      | 400                                             | 450                     | 250                                           |

| Contrast Ratio         | 500:1                                           | 800:1                   | 1000:1                                        |

| Viewing Angle(H/V)     | 170/160                                         | 170/170                 | 178/178                                       |

| Backlight Lifetime     | 50,000hrs                                       | 50,000hrs               | 50,000hrs                                     |

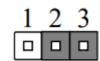

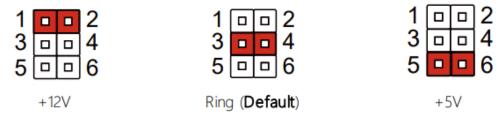

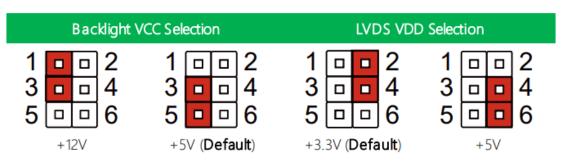

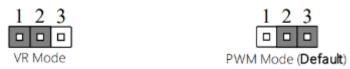

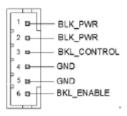

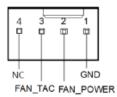

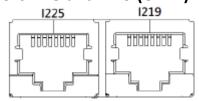

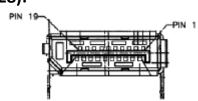

| Option                 |                                                 | Optical                 | bonding                                       |